Competição: Acelerador Blokus Duo

XIV Jornadas Sobre Sistemas Reconfiguráveis, FCT/Universidade Nova de Lisboa, Caparica, 15 Fevereiro 2018

Introdução

-

Blokus Duo é um jogo de tabuleiro (14x14) para 2 jogadores. Cada jogador tem 21 peças diferentes, com diferentes números de “casas”, e que apenas podem ser colocadas no tabuleiro em contacto com os cantos de peças da mesma cor. Só é permitido o contacto de faces entre peças de cor diferente. O jogo termina quando um jogador colocar todas as peças, ou caso não existam mais possibilidades de jogar para nenhum dos jogadores. Ganha o jogador que coloque todas as peças primeiro, ou tiver o menor número de “casas” em sua posse. Neste concurso, destinado a alunos do ensino superior, cada equipa concorre com um jogador Blokus Duo autónomo em FPGA ou Arduino.

Este campeonato é baseado em edições anteriores: ICFPT 2013, HEART2014 e HEART2015. Os ficheiros de apoio e os registos dos jogos das últimas competições encontram-se em Suporte.

Novidades

- 10-Fev: Nova versão do árbitro - resolvido problema do Cygwin não comunicar com o dispositivo na 2ª porta série. Sketch com código minimo para validar competição entre Arduinos.

- 09-Fev: Submissão dos abstracts e posters (aberta até dia 12).

- 09-Fev: IDs das equipas.

- 04-Nov: Suporte para Cygwin. Exemplo do cálculo da pontuação. Outras aplicações adicionadas.

- 07-Out: Novos prémios adicionados.

- 26-Set: Novos prémios adicionados.

- 14-Set: Lançamento da página da competição.

Prémios

- Para os 2 primeiros classificados em cada categoria:

- Pro (FPGA+CPU): DE10-STANDARD (Terasic+Intel FPGA) ou ZynqBerry TE0726 (Trenz+Xilinx)

- Especialista (FPGA): DE10-NANO (Terasic+Intel FPGA) ou ZynqBerry TE0726 (Trenz+Xilinx)

- Novato (Arduino): DE10-LITE (Terasic+Intel FPGA) ou ArduZynq TE0723 (Trenz+Xilinx)

- Melhor poster.

Registos da competição REC2018

- Registos (.zip). (a serem disponibilizados após o evento)

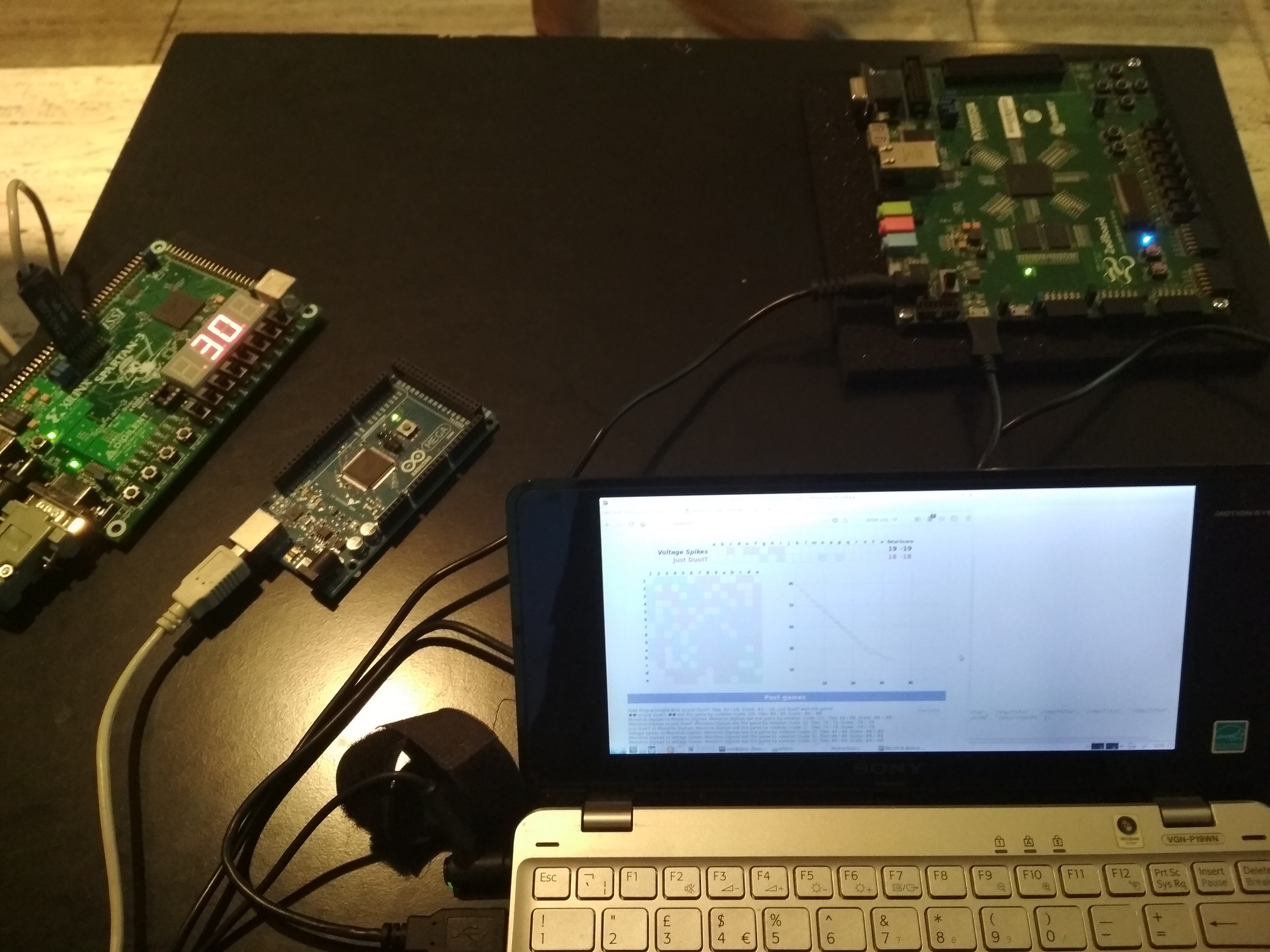

Fotos do evento

Equipas

| ID | Nome da Equipa | Institutição | Categoria | Classificação |

|---|---|---|---|---|

| P1 | Just DuoIT | Instituto de Telecomunicações - Pólo de Aveiro | Pro | 1º |

| P2 | Field Programmable Bros: Blokus Duo SoC | Instituto Superior Tecnico | Pro | 2º |

| E1 | Monstros Digitais | Universidade Nova de Lisboa – FCT | Especialista | 1º |

| E2 | BlokusDuo | Universidade Nova de Lisboa – FCT | Especialista | - |

| N1 | Blokic | Universidade Nova de Lisboa – FCT | Novato | 2º |

| N2 | Voltage Spikes | Universidade Nova de Lisboa – FCT | Novato | 1º |

Categorias de competição

O objectivo desta competição é desafiar a comunidade de sistemas reconfiguráveis Portuguesa, e captar o interesse dos mais jovens para a área. Para tal, foram criadas três categorias: "Novato", "Especialista" e "Pro". Nesta competição tanto podem participar soluções baseadas em RTL como em HLS/openCl.

- Apenas placas Arduino. CPU Clk <= 16MHz (exemplo: UNO)

- Apenas placas FPGA básicas. Incluindo Arria/Cyclone, Spartan/Artix FPGAs. Inclui soft-CPU (NIOS, MicroBlaze).

- FPGA+CPU: Altera/Intel Cyclone V SoC e Xilinx Zynq SoCs.

Novato:

Especialista:

Pro:

Participação / Submissões

Para participar na competição deve submeter um artigo ou um abstract, formatado de acordo com as regras da REC 2018.

Submissão via EasyChair (aberta até dia 12). Os posters devem também ser enviados para o email da conferència. Os abstracts (max 2 páginas) não irão constar nos proceedings mas terão uma oportunidade de serem apresentados como poster (dependendo do número de submissões e do espaço disponível no local da conferência). O objectivo é apresentarem o vosso sistema de forma clara e sucinta, explicar qual a estratégia adoptada, e recursos ocupados.

- As equipas são no máximo de 6 pessoas;

- Pre-inscrição da equipa e da categoria via Formulário até dia 14 de Janeiro de 2018, para o email rec2018 (arroba) uninova (ponto) pt;

- A inscrição de pelo menos de um elemento da equipa nas jornadas de acordo com as regras das jornadas REC 2018.

- Data limite de submissão dos abstracts: 10 Fevereiro de 2018 (os artigos cumprem com o prazo das jornadas). É possível fazer actualização da submissão até à data limite. Fazer a submissão o mais cedo possível.;

- Notificação dos autores para atribuição dos IDs: 12 Fevereiro de 2018;

- Para a competição (durante as jornadas), as equipas devem trazer o seu sistema pronto a funcionar e a comunicar via USB (ver Suporte).

- As equipas apresentam o seu poster de forma interactiva (3-5 minutos).

Patrocínios

e

e

Trenz Electronic develops, manufactures, integrates and sells FPGA and SoC modules for business and science. Main focuses are on e.g. application specific HDL and FPGA design plus hard- and software development. All modules produced by Trenz Electronic are developed and manufactured in Germany.

Contactos

- Organização:

- Rui Duarte - Universidade de Lisboa (rui (ponto) duarte (arroba) tecnico (ponto) ulisboa (ponto) pt)

- Anikó Costa - Universidade Nova de Lisboa

- Luis Gomes - Universidade Nova de Lisboa

- José Carlos Alves - Universidade do Porto

- Juri:

- Membros do Comité Científico e de Programa presentes